La struttura dei prezzi delle fonderie di semiconduttori come TSMC varia in base a volumi di produzione e clienti. Apple, ad esempio, potrebbe ottenere tariffe più favorevoli rispetto a concorrenti come AMD e Qualcomm.

Il crescente interesse dei clienti, specialmente per applicazioni di intelligenza artificiale e calcolo ad alte prestazioni, sta spingendo TSMC a potenziare la capacità produttiva dei suoi stabilimenti di Hsinchu e Kaohsiung.

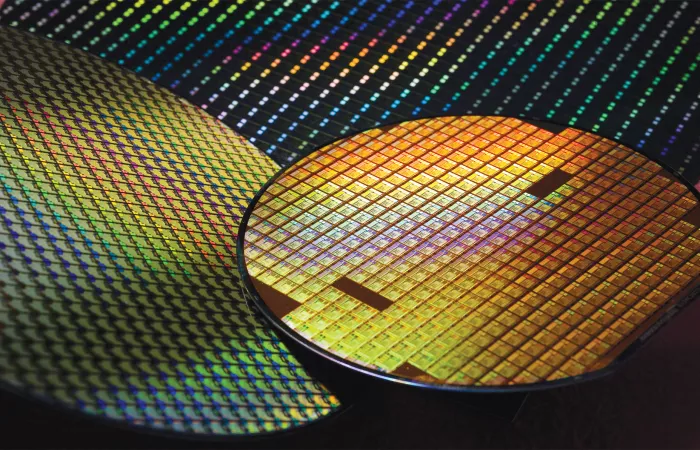

Cosa significa che TSMC potrebbe chiedere fino a $45.000 per wafer per i suoi nodi più avanzati?

TSMC sta considerando di aumentare il prezzo dei wafer per i suoi nodi più avanzati, come l'A16 a 1,6 nm, fino a $45.000 per wafer. Questo rappresenta un incremento del 50% rispetto al nodo N2 precedente, il cui prezzo massimo era di circa $30.000 per wafer. L'aumento è attribuito alla complessità e ai costi associati all'implementazione di tecnologie avanzate come la rete di alimentazione sul retro del chip (BSPDN).

Cos'è la tecnologia di rete di alimentazione sul retro del chip (BSPDN) e perché è importante?

La rete di alimentazione sul retro del chip (BSPDN) è una tecnologia che sposta la rete di distribuzione dell'alimentazione dalla parte frontale alla parte posteriore del wafer di silicio. Questo approccio migliora l'integrità dell'alimentazione, riduce le interferenze dei segnali e aumenta le prestazioni complessive dei circuiti integrati. TSMC ha introdotto questa tecnologia nel suo nodo A16 per migliorare l'efficienza e le prestazioni dei chip destinati ad applicazioni di intelligenza artificiale e calcolo ad alte prestazioni.

Perché Apple potrebbe ottenere tariffe più favorevoli rispetto ad altri clienti di TSMC?

La struttura dei prezzi di TSMC varia in base ai volumi di produzione e ai clienti. Apple, essendo uno dei principali clienti di TSMC con ordini di grandi volumi, potrebbe negoziare tariffe più favorevoli rispetto ad altri concorrenti come AMD e Qualcomm. Questo vantaggio deriva dalla capacità di Apple di garantire ordini consistenti e di lungo termine, che offrono a TSMC una maggiore stabilità e prevedibilità nella produzione.

Quali sono le sfide associate all'implementazione della tecnologia BSPDN nei processi di produzione dei semiconduttori?

L'implementazione della tecnologia BSPDN presenta diverse sfide, tra cui la necessità di riprogettare la rete di distribuzione dell'alimentazione e di sviluppare nuovi metodi di gestione termica, poiché i punti caldi del chip si trovano ora sotto una rete di fili, complicando la dissipazione del calore. Inoltre, richiede l'adozione di nuovi strumenti EDA e software di simulazione aggiornati per supportare il nuovo flusso di progettazione.

Come si confronta la tecnologia Super Power Rail di TSMC con la tecnologia PowerVia di Intel?

La tecnologia Super Power Rail (SPR) di TSMC e la tecnologia PowerVia di Intel sono entrambe soluzioni di rete di alimentazione sul retro del chip (BSPDN). Tuttavia, SPR collega direttamente la rete di alimentazione posteriore alle sorgenti e ai drain dei transistor, riducendo la resistenza e migliorando l'efficienza energetica, ma con una maggiore complessità di produzione. PowerVia di Intel, invece, collega l'alimentazione al contatto della cella o del transistor, offrendo benefici simili ma con una complessità di produzione leggermente inferiore.

Quali sono i benefici attesi dall'adozione della tecnologia A16 di TSMC per le applicazioni di intelligenza artificiale?

L'adozione della tecnologia A16 di TSMC, che include transistor nanosheet GAAFET e la rete di alimentazione sul retro del chip (BSPDN), è progettata per migliorare le prestazioni e l'efficienza energetica dei chip. Si prevede un aumento delle prestazioni dell'8%-10% alla stessa tensione e complessità, o una riduzione del consumo energetico del 15%-20% alla stessa frequenza e numero di transistor. Questi miglioramenti sono particolarmente vantaggiosi per le applicazioni di intelligenza artificiale e calcolo ad alte prestazioni, dove l'efficienza energetica e le prestazioni sono cruciali.